https://dx.doi.org/10.12785/ijcds/120184

# High Throughput Efficient Implementation of Grain v1, Lizard and Plantlet Stream Ciphers for Resource Constraint Devices

Vinod Kumar Gill<sup>1</sup>, Ravi Teja Chenna<sup>2</sup>, Naveen Kumar Kandula<sup>3</sup> and Dheeraj Kumar Sharma<sup>4</sup>

<sup>1,2,3</sup>Department of School of VLSI Design Embedded System, National Institute of Technology Kurukshetra, Haryana, India <sup>4</sup>Department of Electronics Communication Engineering, National Institute of Technology Kurukshetra, Haryana, India

Received 22 Jan. 2021, Revised 15 Jul. 2022, Accepted 23 Jul. 2022, Published 31 Oct. 2022

Abstract: Nowadays, as the number of smart devices is increasing, technologies like Radio Frequency Identification (RFID) and the Internet of Things (IoT) are playing a vital role in communicating among various smart devices which require high security for the data transmission using fewer resources effectively. To implement security with fewer resources available, one of the methods is to use lightweight cryptographic algorithms. Cipher is one of the cryptographic algorithms, which uses the key for encryption and decryption. This paper describes three lightweight symmetric stream ciphers, Grain v1, Lizard, and Plantlet, and their different versions. These versions are implemented on various Field Programmable Gate Array (FPGA) boards such as Kintex7, Virtex7, and Zynq, and their simulations, synthesis, and implementations are performed with the help of Xilinx ISE using Verilog Hardware Description Language (HDL). The area, frequency, throughput, and throughput per area are compared among the different versions of the same cipher and also with existing literature. To generate keystream bits, Grain v1 uses 161 clocks in the basic version, 320 clocks in the serial version, and 11 clocks in the parallel version, Lizard uses 258 clocks in the basic version, 499 clocks in the serial version and 46 clocks in parallel version and Plantlet uses 321 clocks in the basic version and 491 clocks in serial version. The parallel version provides high throughput than the basic and serial versions as the keystream bits generated in each clock cycle are more. Among these versions, the parallel version of Grain v1 and Lizard gave the highest throughput of 9147 and 2412 Mbps along with throughput per area of 50.81 and 9.28 respectively. The parallelism helps in achieving faster data transfer and high operating frequency ranges which is more suitable for the present emerging technologies IOT, blockchains, and Ultra High Frequency Radio Frequency Identification (UHF-RFID).

Keywords: IoT, Resource Constrained Devices, RFID, FPGA, Stream Cipher, Grain v1, Lizard, Plantlet

# 1. INTRODUCTION

From the past decade, as the digital era came into existence, the internet and communication technologies like the Internet of Things (IoT), Radio Frequency Identification (RFID), etc used to communicate among various smart devices have become an important part of our daily lives. Since the usage of smart devices is increasing, the major problems are storage and security. The technologies like IoTs and RFID have to perform effectively using fewer resources with high security. To implement security with fewer resources available, one of the methods is to use lightweight cryptographic algorithms. Cryptography is the oldest technique used which includes encryption and decryption of data. Encryption is converting the source data to a secured and unintelligible form and decryption is converting the unintelligible form of data to the source data. Ciphers are used in cryptography, which are algorithms used for encryption and decryption using a key. Based on the key, the ciphers can be categorized into two types: symmetric and asymmetric. In asymmetric ciphers, the public key is used at the time of encryption and the secret key is used at the time of decryption whereas in symmetric ciphers, during encryption and

decryption process, the same secret key is used.

Symmetric ciphers are mainly divided into two categories: block cipher and stream cipher. Block cipher is a technique that divides the information into a set of fixed length of blocks and then encrypt and decrypt each block. In the stream cipher, the information is bit by bit encrypted and decrypted by using the generated key bitstream. Stream ciphers have an advantage over the block ciphers since the information can be directly encrypted whereas, in the block ciphers, the information has to be stored in memory to divide the information into blocks. Some of the applications of stream ciphers are RFID tags, multi-gigabit communication channels, radio communication, and Global System for Mobile Communications (GSM) communication.

The Grain family (Grain v0, Grain v1, Grain 128a)[1], [2], [3] is one of the portfolios of the stream ciphers, which was accepted in eSTREAM [4]. For the first time, it was submitted by M. Hell, T. Jonasson, and W. Meier [5] in the year 2005. Grain 128AEAD [6] is the latest entry in the Grain family and it is based on Grain 128a

*E-mail address: vinod\_32018240@nitkkr.ac.in, ravi\_32018226@nitkkr.ac.in, naveen\_32018222@nitkktpac/ipurnals.uob.edu.bh sharma986dheeraj@nitkkr.ac.in*

[3] to add extra security. This family consists of a LFSR (linear feedback shift register) and a NFSR (non-linear feedback shift register) which were designed to achieve a high speed at the cost of the additional hardware requirement. The LFSR assures periodicity or steadiness of the output whereas the non-linearity is introduced by the NFSR. The motivation behind that research was to provide security for RFID tags, where memory and power are limited. This design was referred to as Grain v0. Based on this idea, many designs were proposed. One of the designs proposed was Grain v1, which contains 64 bit initialization vector (IV) and 80 bit secret key including a 160 bits of internal state. Grain v1 has a similar design to Grain v0. It uses the same LFSR polynomial function used in Grain v0, but the NFSR polynomial function is different and provides more reliability. For each key/IV pair, a keystream of length 238 is produced in Grain v1 [7].

Hamann, M., Krause, M., Meier, W [8] proposed a Lizard cipher to get attractive features regarding security and efficiency. Specifically, packet mode scenarios are targeted. Lizard is a lightweight stream cipher which is specially designed for limited power resource devices. The design of Lizard is mostly similar to Grain v1. It consists of a 120 bit secret key, 64 bit IV and 121 internal states. It has two NFSRs instead of LFSR, and NFSR when compared to Grain v1 and some parts of the operation are similar to Grain v1. For every key/IV pair 218 keystream bits are obtained [9].

V. Mikhalev, F. Armknecht, and C. Müller proposed a Plantlet [10] cipher from the sprout [11] cipher which stores a non-volatile key. Plantlet is a lightweight cipher and has a larger size of LFSR which overcomes the weaknesses in sprout cipher since, Plantlet has 61 bit LFSR and sprout has 40 bit LFSR. Plantlet also provides more security. Plantlet works on the double layer LFSR and there is no all zero state in the LFSR. Plantlet consists of a 80 bit secret key and 90 bit IV. It has LFSR of size 61 bit and NFSR of size 40 bit and a od 80 counter. It has few modifications in the functions of the sprout cipher but the operation is similar in both the ciphers. One Key/IV pair is used to generate 230 keystream bits [10].

The above mentioned ciphers are implemented using Xilinx ISE Design Suite 14.7 [12]. It is a very useful Electronic Design Tool (EDA) tool which consists of synthesis and implementation. It also generates Register Transfer Level (RTL) schematics, technical schematics and simulation results, which are used to understand the behavior of code on various FPGA boards. It also generates a design summary after synthesis and implementation. RTL schematic is also known as the gate-level schematic which gives an overview consisting of logic gates, adders, etc., based on code and it is independent of the selected device. Technical schematic gives an overview consisting of a number of look up tables (LUT), buffers, flip flops, etc., and it is generated based on the selected devices. Simulation is used to verify the design based on the stimulus applied and monitor for the desired output results.

FPGAs [13] have advantages over ASIC [14] in various domains such as reusable memory and reconfigurable devices and, are used in various applications like Radio Detection and Ranging (RADAR) [15]. Smart Medical [16], Cloud Computing [17] and Data Centre Programs [18] etc. Xilinx ISE Design suite supports many FPGA boards. In this work, the 7 series FPGA boards such as Kintex7 [19], Virtex7 [20] and Zynq [21] are used. Kintex7 [19] is a low cost FPGA with a high end performance built on a 28 nm architecture designed for maximum power efficiency and it consumes 50 less power compared to previous generations of FPGAs. It supports mainstream standards like Peripheral Component Interconnect (PCI) gen3 and 10 gigabit ethernet and it can be used in 3G and 4G wireless, video over IP solutions. Virtex7 [20] is an FPGA board built on 28 nm architecture designed to achieve high I/O bandwidths and high Digital Signal Processing (DSP) performance and it can be used in 10G to 100G networking, portable radars etc. Zynq 7000 [21] consists of a dual core ARM processor equipped with 28 nm Kintex7 [19] based programmable logic and has 6.6 million logic cells. It is used in various embedded applications like multi camera drivers, HDTV, etc.

In the present work, the above described ciphers are implemented in various versions i.e., Grain v1 and Lizard are implemented in basic, serial and parallel versions whereas Plantlet is implemented in basic and serial versions. In the basic version, inputs are taken at a time and output keystream is generated bit by bit. In the serial version, inputs are to be taken in bit by bit form and output keystream is produced in the form of bit by bit and in parallel, the inputs are taken all at a time and output keystream is given n bits at a time. n is 16 and 6 for Grain v1 and Lizard, respectively. To achieve high throughput, the parallel version is considered. All these versions have their advantages and disadvantages. They are used accordingly for different performance motives.

The remaining part of the paper is categorized in the following sections. Section 2 includes the working of the three ciphers. Section 3 describes the simulation results of phases present in different versions of ciphers. The implementation of ciphers performed on various FPGA boards is explained in section 4. The drawn conclusions are outlined in section 5.

# 2. WORKING OF CIPHERS

This section describes the working of Grain v1, Lizard and Plantlet stream ciphers. The initialization and keystream generation phase are demonstrated. Further, various versions such as basic, serial and parallel are described. It has been outlined in the following subsections.

# A. Grain v1

Grain v1 [6] is a symmetric stream cipher which takes 80 bits secret key and 64 bits IV as inputs and processes them to generate a keystream. It consists of two 80 bits shift registers i.e., LFSR whose states are represented as  $M_1 = m_{l_l}, m_{l_{l+1}}, ..., m_{l_{l+79}}$  NFSR whose states are represented as  $N_l = n_{l_l}, n_{l_{l+1}}, ..., m_{l_{l+79}}$  and a non-linear output function  $w(u_1) = w(u_{10}, u_{11}, u_{12}, u_{13}, u_{14})$  which is a five input variable function.

LFSR is a shift register which has linear feedback. In linear feedback, some values from the shift register are added together to generate a value which is given as feedback input to the shift register. Whereas the NFSR is a shift register which has non-linear feedback. In nonlinear feedback some values from the shift register are multiplied and then added together to generate a value which is given as feedback input to the shift register. The non-linear output function takes four inputs from LFSR and one input is taken from NFSR.

Grain v1 works in two phases: initialization phase and keystream generation phase. First in the initialization phase the secret key, IV and 16 padding bits i.e., 16'hFFFF are loaded into the shift registers and for updating the shift registers i.e., the outputs from the feedback function and the output function are added together and then given as feedback to LFSR and NFSR for 160 clock cycles. The feedback function and output functions equations are as mentioned below.

$m1_{l+80} = m1_{l+62} \oplus m1_{1+51} \oplus m1_{l+38} \oplus m1_{l+23} \oplus m1_{l+13} \oplus m1_{l}$

(1)

$$n1_{l+80} = m1_l \oplus n1_{l+62} \oplus n1_{l+60} \oplus n1_{l+52} \oplus n1_{l+45} \oplus n1_{l+37}

\oplus n1_{l+33} \oplus n1_{l+28} \oplus n1_{l+21} \oplus n1_{l+14} \oplus n1_{l+9} \oplus n1_{l}

\oplus n1_{l+63}n1_{l+60} \oplus n1_{l+37}n1_{l+33} \oplus n1_{l+15}n1_{l+9}

\oplus n1_{l+60}n1_{l+52}n1_{l+45} \oplus n1_{l+33}n1_{l+28}n1_{l+21}

\oplus n1_{l+60}n1_{l+52}n1_{l+37}n1_{l+33}$$

(2)

$\oplus n1_{l+60}n1_{l+52}n1_{l+37}n1_{l+33}n1_{l+28}n1_{l+21}

\oplus n1_{l+63}n1_{l+45}n1_{l+37}n1_{l+33}n1_{l+28}n1_{l+21}

\oplus n1_{l+63}n1_{l+60}n1_{l+21}n1_{l+15}n1_{l+9}

\oplus n1_{l+63}n1_{l+60}n1_{l+21}n1_{l+15}$

$$x_{l} = W(M_{l}, N_{l})$$

(3)

=  $\bigoplus_{i \in A} n \mathbf{1}_{l+j} \oplus w(n \mathbf{1}_{l+3}, n \mathbf{1}_{l+25}, n \mathbf{1}_{l+46}, n \mathbf{1}_{l+64}, n \mathbf{1}_{l+63})$

where A=1,2,4,10,31,43,56

$$w(u1) = w(u1_0, u1_1, u1_2, u1_3, u1_4)$$

=  $u1_1 \oplus u1_4 \oplus u1_0 u1_3 \oplus u1_2 u1_3 \oplus u1_3 u1_4$  (4)

$\oplus u1_0 u1_1 u1_2 \oplus u1_0 u1_2 u1_3 \oplus u1_0 u1_2 u1_4$

$\oplus u1_1 u1_2 u1_4 \oplus u1_2 u1_3 u1_4$

During the initialization phase, no keystream output is taken from the cipher. Key bit stream generation phase is the second phase. In this phase, the only input to the shift registers is from the feedback functions and the output keystream is generated from the non-linear output function.  $m1_{l+80}$  is the feedback function used to update LFSR and  $n1_{l+80}$  is the feedback function used to update NFSR.  $x_l$  is the output function.

Grain v1 can be implemented in three versions: basic,

serial and parallel based on the incoming inputs and as well as the required output bit stream. In the basic version, during the loading stage, the secret key and IV pair (with padding bits) are taken all at a time in a single clock cycle. The output from the feedback function and the output function are produced bit by bit. In the serial version, while loading the secret key, IV and the padding bits, the bits are loaded into shift registers bit by bit. It takes 160 clock cycles to load all the bits. The output is generated in a similar manner as provided in the basic version.

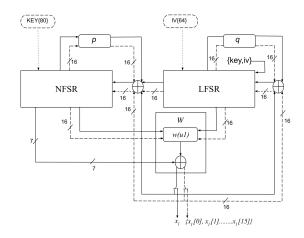

Figure 1. Block Diagram of Grain v1

In the parallel version, inputs are taken in a similar manner as the basic version i.e., in one clock cycle and the output from the feedback function and the keystream output generates 16 bits in one clock cycle since the maximum possible parallelism is 16. In the parallel version the shift registers are updated by 16 bits for every clock cycle. In the initialization phase, it requires 160 clock cycles to update both the shift registers since in the parallel version, authors have taken 16 bits at a time and therefore, only 10 clock cycles are required In Figure 1, p and q represent feedback functions of NFSR and LFSR respectively. While loading the inputs i.e., secret key and IV, dotted lines represent basic and parallel versions and solid lines represent serial versions. In the remaining part of the operation, the solid lines represent basic and serial versions and dashed lines represent parallel versions, the shift registers are updated by 16 bits for every clock cycle. In the initialization phase, it requires 160 clock cycles to update both the shift registers since in the parallel version, authors have taken 16 bits at a time and therefore, only 10 clock cycles are required.

In Figure 1, p and q represent feedback functions of NFSR and LFSR respectively. While loading the inputs i.e., secret key and IV, dotted lines represent basic and parallel versions and solid lines represent serial versions. In the remaining part of the operation, the solid lines represent basic and serial versions and dashed lines represent parallel versions.

#### B. Lizard

Lizard [8] is a symmetric stream cipher which takes 120 bits secret key and 64 bit IV as inputs and processes them to generate the keystream. The process

of generating keystream consists of key register, shift registers, feedback functions and output functions. Two NFSRs of size 90  $(m_0^l, m_1^l, m_2^l, m_3^l, \dots, m_{88}^l, m_{89}^l)$  and 31 bits  $(n_0^l, n_1^l, n_2^l, n_3^l, \dots, m_{29}^l, n_{30}^l)$  are used in the Lizard. The output function  $(z_l)$  is also a nonlinear function which takes values from both shift registers.

In Lizard, the operation basically has two phases: initialization phase and keystream generation phase. The initialization phase is again divided into four phases i.e., key IV loading phase, NFSRs updating phase, second key addition phase and final diffusion phase. In the Key IV loading phase, the secret key is stored in the key register and key values are added with IV, they are further loaded into NFSR2  $(m_0^l, m_1^l, m_2^l, m_3^l, \dots, m_{88}^l, m_{89}^l)$ . The remaining key values are loaded into NFSR1  $(n_0^l, n_1^l, n_2^l, n_3^l, \dots, n_{29}^l, n_{30}^l)$ . The MSB of NFSR1 is considered binary 1 i.e., 1'b1. In the NFSRs updating phase, the outputs from the feedback function and output function  $(z_l)$  are added together and given as input to NFSRs. This phase is similar to the initialization phase in Grain v1. Thus, this phase is also termed as a Grain like mixing phase. This phase runs for 128 clock cycles. In the second key adding phase, the key stored in the key register is added with the values present in the NFSRs and stored in the NFSRs. In the final diffusion phase, the NFSRs are updated only with the feedback functions and it runs for 128 clock cycles. The feedback and output functions are modified as given below.

Key IV Loading phase:

$$m_{i}^{0} = \begin{cases} K_{i} \oplus IV_{i} & for \ i = \{0, 1, \dots 63\} \\ K_{i} & for \ i = \{64, 65, \dots 89\} \end{cases}$$

(5)

$$n_{i}^{0} = \begin{cases} K_{i+90} & for \ i = \{0, 1, \dots 28\} \\ 1 \oplus K_{119} & for \ i = 29 \\ 1 & for \ i = 30 \end{cases}$$

Second Key Loading phase:

$$m_i^{129} = K_i \oplus m_i^{128} \quad for \quad i = \{0, 1, \dots 89\}$$

(6)

$$n_i^{129} = \begin{cases} K_{i+90} \oplus n_i^{128} & for \quad i = \{0, 1, \dots 29\} \\ 1 & for \quad i = 30 \end{cases}$$

NFSRs Updating feedback Functions:

$$\begin{split} m_{i}^{l+1} &= m_{i+1}^{l} \quad for \quad i = \{0, 1, \dots 88\} \\ m_{89}^{l+1} &= n_{0}^{l} \oplus m_{0}^{l} \oplus m_{24}^{l} \oplus m_{49}^{l} \oplus m_{79}^{l} \oplus m_{84}^{l} \oplus m_{3}^{l} m_{59}^{l} \\ &\oplus m_{10}^{l} m_{12}^{l} \oplus m_{15}^{l} m_{16}^{l} \oplus m_{25}^{l} m_{53}^{l} \oplus m_{35}^{l} m_{42}^{l} \\ &\oplus m_{55}^{l} m_{58}^{l} \oplus m_{60}^{l} m_{74}^{l} \oplus m_{20}^{l} m_{22}^{l} m_{23}^{l} \\ &\oplus m_{62}^{l} m_{68}^{l} m_{72}^{l} \oplus m_{77}^{l} m_{80}^{l} m_{81}^{l} m_{83}^{l} \end{split}$$

(7)

$$n_{i}^{l+1} = n_{i+1}^{l} \quad for \quad i = \{0, 1, \dots 29\}$$

$$n_{30}^{l+1} = n_{0}^{l} \oplus n_{2}^{l} \oplus n_{5}^{l} \oplus n_{6}^{l} \oplus n_{15}^{l} \oplus n_{18}^{l} \oplus n_{25}^{l} \oplus n_{14}^{l} n_{19}^{l} \oplus (n_{12}^{l}(n_{21}^{l} \oplus (n_{19}^{l}n_{22}^{l}(1 \oplus n_{21}^{l})))) \oplus (n_{17}^{l}(1 \oplus n_{21}^{l}))) \oplus (n_{12}^{l}(n_{19}^{l} \oplus (n_{19}^{l}n_{22}^{l}(1 \oplus n_{21}^{l})))) \oplus (n_{17}^{l}(1 \oplus n_{21}^{l}))) \oplus (n_{19}^{l}n_{19}^{l} \oplus (n_{19}^{l}n_{21}^{l} \oplus (n_{19}^{l}n_{21}^{l}))) \oplus (n_{17}^{l}(1 \oplus n_{21}^{l}))) \oplus (n_{19}^{l}n_{19}^{l}n_{21}^{l}) \oplus (n_{19}^{l}n_{21}^{l}) \oplus (n_{19}^{l}n_{21}^{l}) \oplus (n_{19}^{l}n_{21}^{l})) \oplus (n_{19}^{l}n_{19}^{l}n_{21}^{l}) \oplus (n_{19}^{l}n_{21}^{l}) \oplus (n_{19}^{l}n$$

$$\begin{array}{l} \oplus (n_{7}^{l}n_{21}^{l}(n_{20}^{l} \oplus (n_{8}^{l}n_{18}^{l}) \oplus (n_{8}^{l}n_{20}^{l}) \oplus (n_{19}^{l}n_{12}^{l}))) \\ \oplus (n_{4}^{l}(n_{22}^{l} \oplus (n_{7}^{l}n_{21}^{l}) \oplus (n_{21}^{l}n_{22}^{l})) \oplus (n_{12}^{l}n_{19}^{l})) \\ \oplus ((n_{8}^{l}n_{18}^{l} \oplus (n_{20}^{l}n_{8}^{l}) \oplus n_{20}^{l})(1 \oplus (n_{22}^{l}(1 \oplus n_{21}^{l})))) \end{array}$$

$\oplus n_{21}^l))$

Output Function:

$$z_l = T_l \oplus Q_l \oplus P_l \oplus R_l$$

where

$$\begin{split} T_{l} &= m_{7}^{l} \oplus m_{11}^{l} \oplus m_{30}^{l} \oplus m_{40}^{l} \oplus m_{45}^{l} \oplus m_{54}^{l} \oplus m_{71}^{l} \\ Q_{l} &= m_{4}^{l} m_{21}^{l} \oplus m_{9}^{l} m_{52}^{l} \oplus m_{18}^{l} m_{37}^{l} \oplus m_{44}^{l} m_{76}^{l} \\ P_{l} &= m_{5}^{l} \oplus m_{8}^{l} m_{82}^{l} \oplus m_{34}^{l} m_{67}^{l} m_{73}^{l} \oplus m_{2}^{l} m_{28}^{l} m_{41}^{l} m_{65}^{l} \\ &\oplus m_{13}^{l} m_{29}^{l} m_{50}^{l} m_{64}^{l} m_{75}^{l} \oplus m_{6}^{l} m_{14}^{l} m_{26}^{l} m_{32}^{l} m_{47}^{l} m_{61}^{l} \\ &\oplus m_{1}^{l} m_{19}^{l} m_{27}^{l} m_{43}^{l} m_{57}^{l} m_{66}^{l} m_{78}^{l} \\ R_{l} &= n_{23}^{l} \oplus n_{3}^{l} n_{16}^{l} \oplus n_{9}^{l} n_{13}^{l} m_{48}^{l} \oplus n_{1}^{l} n_{24}^{l} m_{38}^{l} m_{63}^{l} \end{split}$$

(8)

In the initialization phase, no keystream output is taken from the cipher. The next phase is the keystream generation phase in which the NFSRs are updated only from the feedback functions. The output from the output function  $(z_l)$  is given as the keystream of the Lizard cipher.

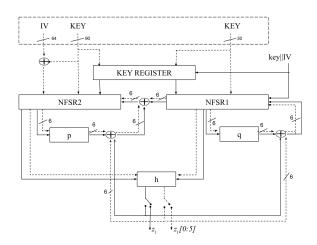

Figure 2. Block Diagram of Lizard

Lizard can be implemented in three versions: basic, serial and parallel based on the inputs and as well as the required output keystream. In the basic version, during the loading phase, the secret key and IV are loaded into the key register, shift registers as mentioned in the equations in a single clock cycle. The outputs from the feedback function and the output function  $z_l$  are given bit by bit. In the serial version during the loading phase, the secret key is loaded into the key registers bit by bit and it takes 120 clock cycles to load all the data. The output is given in a similar manner as the basic version. In the parallel

version, inputs are taken in a similar manner as the basic version in a single clock cycle. The outputs from the feedback function and the output function  $(z_l)$  are given 6 bits in one clock cycle since the maximum parallelism is 6. The shift registers are updated 6 bits for every clock cycle. In the NFSRs updating phase and final diffusion phase, it needs 128 clock cycles to update both the shift registers as in the parallel version, it requires 6 bits at a time. Therefore, only 21 clock cycles are required i.e., 20 clock cycles for updating 120 bits and 1 clock cycle for updating 2 bits.

In Figure 2, p and q represent feedback functions of NFSR2 and NFSR1 respectively. The h represents output function. While loading the inputs i.e., Key and IV, dashed lines represent basic and parallel versions and solid lines represent serial versions. In the remaining part of the operation, the solid lines represent basic and serial versions and dashed lines represent parallel versions.

#### C. Plantlet

Plantlet [10] is a symmetric stream cipher which takes 80 bit secret key and 90 bit IV as inputs and processes them to generate the keystream. The process of generating keystream consists of key register, counter, key selector, shift registers, feedback functions and output functions. The LFSR and NFSR in Plantlet have a size of 61 bit  $(s_{l+0}, s_{l+1}, s_{l+2}, s_{l+3}...s_{l+59}, s_{l+60})$  and 40 bit  $(b_{l+0}, b_{l+1}, b_{l+2}, b_{l+3}...b_{l+38}, b_{l+39})$  respectively. The non-linear output function consists of nine input variables in which seven inputs are taken from LFSR and two inputs are taken from NFSR. The 80 bit secret key is stored in the key register and the counter  $(c_{l+0}, c_{l+1}, c_{l+2}, c_{l+3}...c_{l+78}, c_{l+79})$  is a MOD-80 counter. The key selector  $(k_s)$  is used to select a key bit.

Plantlet works in two phases: initialization phase and keystream generation phase. First, in the initialization phase, the secret key is loaded into the key register, and IV along with the 11 padding bits i.e., 11'h7FD are loaded into the shift registers i.e. the NFSR is loaded with the first 40 bits of IV and next 50 bits of IV are loaded into the first 50 LFSR stages along with 11 padding bits added in remaining LFSR stages. After loading, the 60th bit of LFSR ( $s_{l+59}$ ) is updated by adding the outputs from the feedback function ( $P(S_l)$ ) and the output function ( $Z_l$ ) the 4th MSB from the counter ( $c_{l+4}$ ) and the key selector value ( $k_s$ ). This process continues upto 320 clock cycles. The feedback function and output functions equations are as mentioned below.

In the initialization phase:

$s_{l+59} = z_l \oplus P(S_1)$

where

$$P(S_l) = s_{l+54} \oplus s_{l+43} \oplus s_{l+34} \oplus s_{l+20} \oplus s_{l+14} \oplus s_{l+0}$$

$$Z_l = S_{l+30} \oplus \sum_{j \in A} b_{l+j} \oplus r(B_l, S_l)$$

where

$$A = \{1, 6, 15, 17, 23, 28, 34\}$$

and

$$r(B_l, S_l) = b_{l+4}s_{l+6} \oplus s_{l+8}s_{l+10} \oplus s_{l+32}s_{l+17} \\ \oplus s_{l+19}s_{l+23} \oplus b_{l+4}s_{l+32}b_{l+38}$$

$$b_{l+39} = Z_l \oplus q(B_l) \oplus k_s \oplus S_{l+0} \oplus c_{l+4}$$

(9)

where

$$q(B_{l}) = b_{l+0} \oplus b_{l+13} \oplus b_{l+19} \oplus b_{l+35} \oplus b_{l+39} \oplus b_{l+2}b_{l+25} \\ \oplus b_{l+3}b_{l+5} \oplus b_{l+7}b_{l+8} \oplus b_{l+14}b_{l+21} \oplus b_{l+16}b_{l+18} \\ \oplus b_{l+22}b_{l+24} \oplus b_{l+26}b_{l+32} \oplus b_{l+33}b_{l+36}b_{l+37}b_{l+38} \\ \oplus b_{l+0}b_{l+11}b_{l+12} \oplus b_{l+27}b_{l+30}b_{l+31} \\ h = h_{22} = a_{l+12}a_{l+12}a_{l+12}a_{l+12}a_{l+12}a_{l+13}a_{l+36}a_{l+38}a_{l+16}a_{l+18}a_{l+16}a_{l+18} \\ \oplus b_{l+0}b_{l+11}b_{l+12} \oplus b_{l+27}b_{l+30}b_{l+31} \\ h = h_{22} = a_{l+12}a_{l+12}a_{l+12}a_{l+12}a_{l+16}a_{l+16}a_{l+18}a_{l+16}a_{l+18}a_{l+16}a_{l+18}a_{l+16}a_{l+18}a_{l+16}a_{l+18}a_{l+16}a_{l+18}a_{l+16}a_{l+18}a_{l+16}a_{l+18}a_{l+16}a_{l+18}a_{l+16}a_{l+18}a_{l+16}a_{l+18}a_{l+16}a_{l+18}a_{l+16}a_{l+18}a_{l+16}a_{l+18}a_{l+16}a_{l+18}a_{l+16}a_{l+18}a_{l+16}a_{l+18}a_{l+16}a_{l+18}a_{l+16}a_{l+18}a_{l+16}a_{l+18}a_{l+16}a_{l+18}a_{l+16}a_{l+18}a_{l+16}a_{l+18}a_{l+16}a_{l+18}a_{l+16}a_{l+18}a_{l+16}a_{l+18}a_{l+18}a_{l+16}a_{l+18}a_{l+18}a_{l+16}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a_{l+18}a$$

k<sub>s</sub> = key selector of keyregister according to count value

$$c_{l+4} = MOD \ 80 \ counter \ 4^{th} \ LS \ B$$

In keystream generation phase:

$$s_{l+59} = P(S_1)$$

where

$$P(S_{l}) = s_{l+54} \oplus s_{l+43} \oplus s_{l+34} \oplus s_{l+20} \oplus s_{l+14} \oplus s_{l+0}$$

$$b_{l+39} = q(B_l) \oplus k_s \oplus S_{l+0} \oplus c_{l+4} \tag{10}$$

where

$$q(B_{l}) = b_{l+0} \oplus b_{l+13} \oplus b_{l+19} \oplus b_{l+35} \oplus b_{l+39} \oplus b_{l+2}b_{l+25} \\ \oplus b_{l+3}b_{l+5} \oplus b_{l+7}b_{l+8} \oplus b_{l+14}b_{l+21} \oplus b_{l+16}b_{l+18} \\ \oplus b_{l+22}b_{l+24} \oplus b_{l+26}b_{l+32} \oplus b_{l+33}b_{l+36}b_{l+37}b_{l+38} \\ \oplus b_{l+0}b_{l+11}b_{l+12} \oplus b_{l+27}b_{l+30}b_{l+31}$$

$k_s = key \ selector \ of \ key register \ according \ to \ count value$

$$c_{l+4} = MOD \ 80 \ counter \ 4^{th} \ LS B$$

During the initialization phase, no output keystream generated from the cipher. After this phase, the keystream generation phase is started. The 61th bit of LFSR ( $s_{l+60}$ ) is updated excluding the output from the output function and NFSR is also updated excluding the output from the output function. In this phase, the output of the output function ( $Z_l$ ) is considered as the output of the cipher.

Plantlet can be implemented in two versions: basic and serial. In the basic version, the shift registers and secret key bits are loaded in one clock cycle and the keystream in the keystream generation phase is generated bit by bit i.e., one bit per cycle. In the serial version, the inputs are loaded to the key register and shift registers bit by bit and the remaining operation is the same as in the basic version. Here, 170 clock cycles are needed to load the inputs serially bit by bit to shift registers and key registers. One clock cycle is required for the padding bits. Therefore, 171 clock cycles are required and similar output is generated as in the basic version.

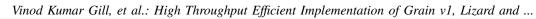

Figure 3. Block Diagram of Plantlet

In Figure 3, p and q represent feedback functions of LFSR and NFSR respectively. The r represents output function. While loading the inputs i.e., secret key and IV, dashed lines represent the basic version and solid lines represent the serial version. In the remaining part of the operation, the solid lines represent basic and serial versions.

# 3. TIME COMPLEXITY

#### A. Grain v1

1056

In Grain V1, the number of the addition and multiplication operations for the LFSR update function, NFSR update function, and Output functions are 5 0, 22 29 and 16 13, respectively. Hence, the total number of addition and multiplication operations in the key generation phase for the GrainV1 are 43 42 respectively. Therefore, the time complexity of the Grain V1 is equal to  $43t_{add} + 42t_{mul} = 43 + 42n^2$ . For basic and serial versions, the time complexity will be  $43 + 42n^2$ . Since, 16 unrolling loops are used in parallel version of GrainV1 therefore time complexity is  $16(43 + 42n^2) = 688 + 672n^2$ .

### B. Lizard

In Lizard, the number of the addition and multiplication operations for the NFSR1 update function, NFSR2 update function, and Output functions are 26 18, 15 14 and 21 31, respectively. Hence, the total number of addition and multiplication operations in the key generation phase for the Lizard are 62 63 respectively. Therefore, the time complexity of the Lizard is equal to  $62t_{add}$  +  $63t_{mul} = 62 + 63n^2$  which is better compared to time complexity of past work [22] i.e,  $67t_{add} + 95t_{mul} = 67 +$  $95n^2$ . For basic and serial versions, the time complexity will be  $62 + 63n^2$ . Since, 6 unrolling loops are used in parallel version of Lizard therefore time complexity is  $6(62 + 63n^2) = 372 + 378n^2$ .

### C. Plantlet

In Plantlet, the number of the addition and multiplication operations for the NFSR update function, LFSR update function, and Output functions are 16 14, 5 0 and 12 6, respectively. Hence, the total number of addition and multiplication operations in the key generation phase for the Plantlet are 36 20 respectively. Therefore, the time complexity of the Plantlet is equal to  $36t_{add} + 20t_{mul} = 36 + 20n^2$ . For basic and serial versions, the time complexity will be  $36 + 20n^2$ .

# 4. SIMULATION RESULTS

# A. Grain v1

Grain v1 stream cipher has three versions i.e., basic, serial and parallel and it works in two phases i.e., initialization phase and key bitstream generation phase. Figures 4-9 show the simulation results of the initialization phase and keystream generation phase for (a) Basic version, (b) Serial version and (c) Parallel version of Grain v1.

Figure 4. Simulation output waveform of initialization phase for Basic version of Grain v1

Figure 5. Simulation output waveform of initialization phase for Serial version of Grain v1

|                                  |                      | 2               | 740 rs           |                 |                |               |                                                                                                                 |                |                  |                 |                   |

|----------------------------------|----------------------|-----------------|------------------|-----------------|----------------|---------------|-----------------------------------------------------------------------------------------------------------------|----------------|------------------|-----------------|-------------------|

| Name                             | Value                | ions .          |                  |                 |                | 14ns          | Pre                                                                                                             |                |                  | pas .           | Pre               |

| la dk                            | a                    |                 |                  |                 |                |               |                                                                                                                 |                |                  |                 |                   |

| lin est                          | 2                    |                 |                  |                 |                |               |                                                                                                                 |                |                  |                 |                   |

| land land                        | 1                    |                 |                  |                 |                |               |                                                                                                                 |                |                  |                 |                   |

| N(62:0)                          | ababododefefabab     | ( )             |                  |                 |                | ababete       | efefabab                                                                                                        |                |                  |                 |                   |

| No ling                          | Ofedcba907654021fedc |                 |                  |                 |                | (feddadd      | 654321/6dc                                                                                                      |                |                  |                 |                   |

| North 194                        | **2-5                | eab5            | i Sce5           | 1 128           | 2602           | 5808          | #891                                                                                                            | \$630          | 4155             | 1 9%de          | 1 2/26            |

| <ul> <li>Mar_fb(15:0)</li> </ul> | 9455                 | 5%f             | 5400             | 6670            | a751           | Sed4          | 63fe                                                                                                            | 1979           | 665              | 551a            | \$401             |

| s80(15)(E                        | Jack                 | Sach            | \$ 9013          | 9.000           | 1 899          | 8(4)          | (230)                                                                                                           | sole           | 5543             | e#Xd            | 8 8662            |

| b00(15:0)                        | fiel                 | 54x1            | 246              | 0188            | Cu4s           | 4990          | 465                                                                                                             | 0497           | a7tb             | 1289            | 9005              |

| N15:0                            | b124                 | 6124            | \$629            | 0.86            | de?            | 0810          | e370                                                                                                            | 4e12           | 896              | 1681            | x 000f            |

| ► 📷 s7900                        | tfffababededefefabab | ITTababcdodef 1 | Aseo HT ababcole | 9113Sactriffaba | 9352903396607  | 1599965590139 | 35403 599455690                                                                                                 | 02008140859994 | Addres/0015408.5 | SHAbadec2028    | relation and real |

| b(790)                           | Ofedoba907454221fedo | 0fectbe3576545  | f4e10fedtba997   | at Rife shedd   | 03502596644306 | 044030005644  | 4250044601532                                                                                                   | 40664050004401 | 04074065409004   | 107050107406540 | 1009170093749     |

| B:0 🖬                            | 10                   | 66              | * *              | 8               | X 7            | 6             | 5                                                                                                               | +              | 3                | 2               | 1                 |

| <ul> <li>M #1530</li> </ul>      | 215e                 | 735e            | actio .          | seli            | diba           | 6740          | 2891                                                                                                            | fcee           | Li Se            | 7141            | 9404              |

| <ul> <li>ext[15:0]</li> </ul>    | 2002                 |                 |                  |                 |                |               | ia di seconda di second |                |                  |                 |                   |

|                                  |                      |                 |                  |                 |                |               |                                                                                                                 |                |                  |                 |                   |

|                                  |                      |                 |                  |                 | -              |               |                                                                                                                 |                |                  |                 |                   |

|                                  |                      | X1: 0.790 rs    |                  |                 |                |               |                                                                                                                 |                |                  |                 |                   |

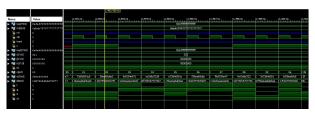

Figure 6. Simulation output waveform of initialization phase for Parallel version of Grain v1

Figure 7. Simulation output waveform of key generation phase for Basic version of Grain v1

The variables present in the simulation results are clk, rst, load, iv, t, key, lfsr'fb, nfsr'fb, s80, b80, h, s, b, i, j, out, z. The variable "clk" is used to denote the clock cycle based on which the operations are performed. "rst" is used to reset which clears all the values in the registers

Figure 8. Simulation output waveform of key generation phase for Serial version of Grain v1

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                       |    |               |                |         | 12.00010 |               |                |                |                  |                |                |              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----|---------------|----------------|---------|----------|---------------|----------------|----------------|------------------|----------------|----------------|--------------|

| Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Value                 | ١. | 10 rs         | 11:55          |         |          |               |                |                |                  |                |                |              |

| lin dk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                     |    |               |                |         |          |               |                |                |                  |                |                |              |

| 1G est                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                       |    |               |                |         |          |               |                |                |                  |                |                |              |

| 1 load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                       |    |               |                |         |          |               |                |                |                  |                |                |              |

| Mising                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ababrefredefefabab    |    |               |                |         |          |               | ababcdcdefi    |                |                  |                |                |              |

| ▶ 11 kep(720)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Ofed:ba997654221fed:  |    |               |                |         |          |               | Ofeecbar20755  | ¢a:fedo        |                  |                |                |              |

| Ischersel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                       |    | \$502         | 5260           | Ì       | 0585     | 5085          | 92e1           | 8225           |                  | 3324           | 368            | 1980         |

| mtu_tb(15x)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                       |    | 1146          | 0.064          |         | 6044     | dief          | 7323           | ŕfab           | 6723             | be29           | 0658           | 1 e010       |

| ► 😻 180(15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                       |    | 1700          | be33           | ) —     | ica2     | dda1          | 3746           | ce3c           | e468             | 0004           | a38a           | 7388         |

| BR001500                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                       |    | 094           | e19            | $\sim$  | 640      | 45ce          | 6684           | 9362           | 1902             | 4094           | 5337           | 1 163        |

| N(15:0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                       |    | 9528          | 4be            | X =     | 350É     | 9492          | 376c           | 7526           | stef             | 2/4            | 4036           | 6946         |

| ► ST910                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12ec51025852e3765943  |    | 0002063059438 | \$50200288705  | 1 50865 | Kille.   | 0588528655720 | 9089058652905  | 9261908905885  | 8/259/2019/08/90 | 4949882590819. | 10049494642259 | 130085308494 |

| ► S(79.0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0464314433166f5b5a?ob |    | 0005855947504 | 13400001930987 | 136683  | accests  | da+065312430  | d5efc0a4065c00 | 7323d5efd3a43d | Hits 232335e152  | 6723Hdb7123d5  | be296723Hdb73  | 30.545423672 |

| 13:01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                       | Ð  |               |                |         |          |               | 0              |                |                  |                |                |              |

| In the second |                       |    | 4162          | 635            | )       | 4924     | 4021          | 1507           | 6419           | ad21             | r36d           | 9862           | ( 663)       |

| ▶ 🖬 ect[15:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       |    | 1000          | 4212           |         | ec95     | e324          | 4021           | 15a7           | 6c13             | ad21           | fibd           | 2662         |